ZM-VF01A is a Voter-module offering radiation protection against Single-Event-Upsets (SEU) with radiation-hardened Voter-IC (ZES400) integrated with Triple-Modular-Redundancy (TMR) Ferroelectric Random Access Memory (FRAM) 1M-bit (3pcs) together with ZES Error-Detection-and-Correction (ZEDAC) C-code software for protection of data stored in the embedded memory (e.g., MCU/FPGA/GPU’s initialization data, config data, user data, etc.) & external high-speed memories (DDR, eMMC).

The ZES400 Voter-IC embodies 4-channel voting circuits where one of the channels is used to TMR voting the outputs of the FRAMs. An additional voter channel is available for supporting TMR for another signal where necessary. The ZM-VF01A features ultra-low errors, and suitable for storing critical data and/or supporting ZEDAC algorithms.

Compact form factor Module (11.8mmx 11.8mm) can easily be plug-in to the existing COTS sub-system (MCU/FPGA/GPU) with minimal design changes to payloads.

Voter-Hardware/ ZEDAC-software co-solution provides Data-integrity protection for memories

ZM-VF01A is integrated with the ZES error-detection-and-correction (ZEDAC) algorithms to enable data protection virtually for any memories (e.g., eMMC or DRR4).

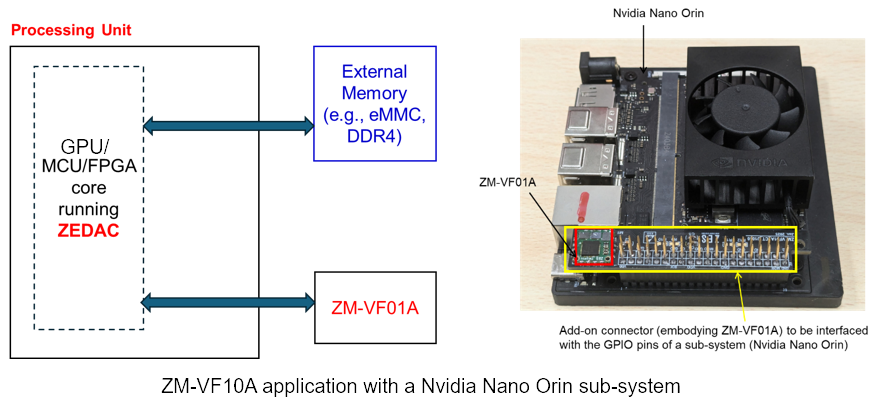

The interface setup where a processing unit embodying either the MCU/FPGA/GPU, is interfaced with an external memory and ZM-VF01A. The external memory could be a Commercial-Off-the-Shelf (COTS) memory (e.g., eMMC or DDR4) whose data need to be protected.

The ZEDAC algorithm is executed within the GPU/MCU/FPGA, providing the encoding/decoding process. The ZM-VF01A and the ZEDAC algorithm collectively serves as hardware/software co-solution to reduce the soft-error (e.g., bit flips) in the external memory, provides 2000x better error-rate solution vs. SECDED (Single-Error-Correction-Double-Error-Detection).

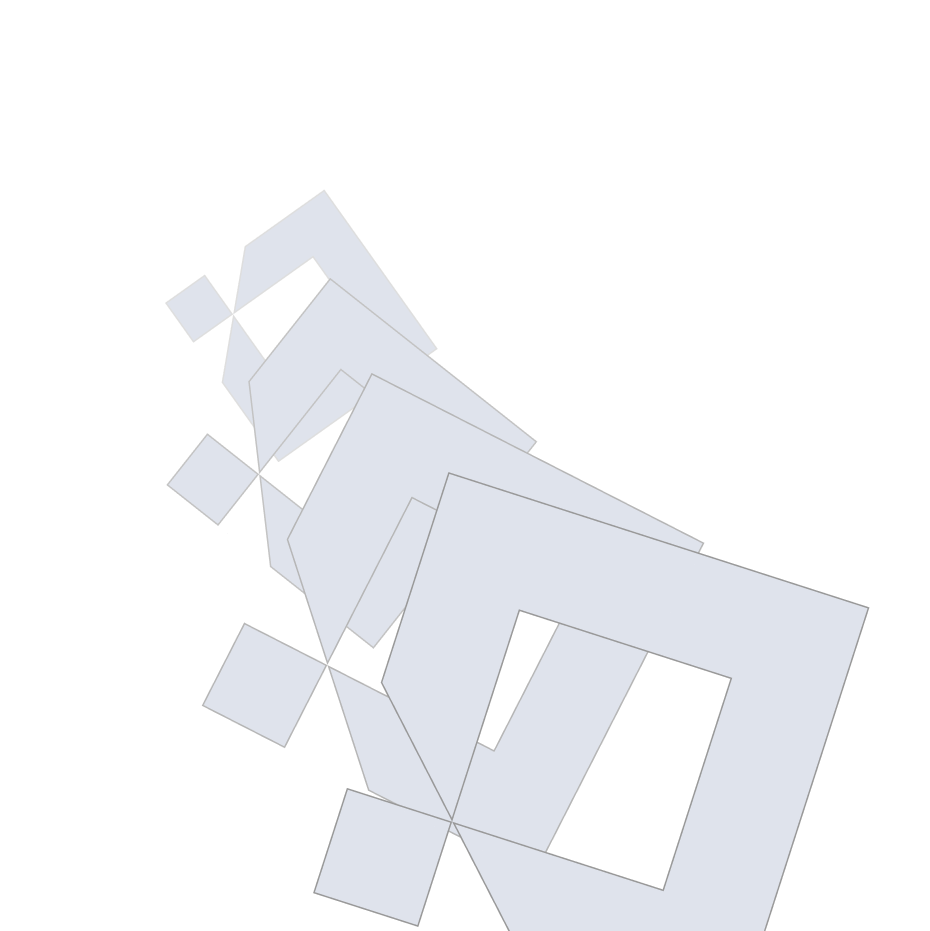

Add-on Connector for Interfacing a NVIDIA Nano Orin GPU System with SPI Ports

ZM-VF01A can be mounted to a customized add-on connector board which can be interfaced with MCU/FPGA/GPU system/subsystem via the GPIO pins.

An example where the add-on connector is designed to embody the ZM-VF01 module, and plug-in to 40-pin interface compatible with a Nvidia Nano Orin GPU sub-system, inherently connected (via the SPI ports) to the MCU.

If necessary, the ZEDAC algorithm can be easily executed in the MCU, checking/recovering the data using the MCU and the ZM-VF01. The data to be protected could be embedded SRAMs within the MCU, or the dedicated eMMC/DDR memories within the Nvidia Nano Orin sub-system.

Similarly, the add-on connector board can be customized for other systems/sub-systems such as Raspberry Pie systems/sub-systems.