Ensuring data integrity in high-speed memory is crucial for maintaining the accuracy and reliability of stored information, especially in radiation-prone environments like space.

Zero-Error Systems implements Triple Modular Redundancy (TMR) through both hardware and software using advanced Error Detection and Correction (EDAC) algorithms to protect against Single Event Upsets (SEU).

Current COTS memories are highly prone to SEUs, with an unacceptably high SER (e.g., 10⁻² to 10⁻⁴ errors per bit per day in harsh environments). Existing redundancy methods for COTS memories may also fall short.

For instance, Triple-Modular-Redundancy (TMR) significantly increases the form factor and complicates connectivity, especially with large data word lengths. Similarly, software-assisted Error-Detection-and-Correction (EDAC) struggles with multi-bit errors due to speed limitations

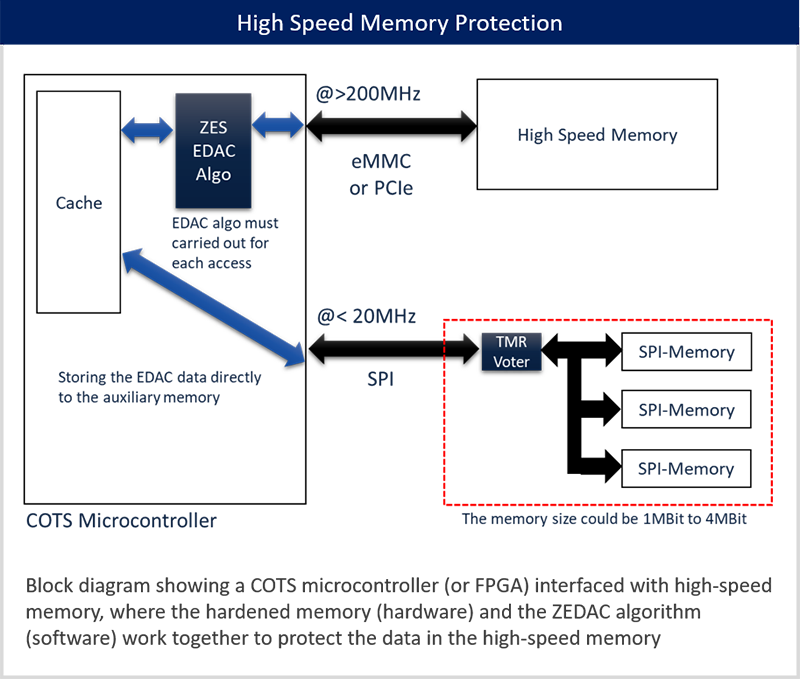

ZES’ patent-pending solution combines hardware and software to protect COTS high-speed memory from SEUs. As shown in Block digram, a COTS microcontroller or FPGA interfaces with high-speed memory (e.g., DDR, eMMC, Flash) and a low pin-count hardened memory via SPI.

The hardened memory, protected by TMR with a ZES400 voter, keeps hardware overhead minimal. Our ZES EDAC (ZEDAC) is a C-code library that encodes and decodes data in both high-speed and hardened memory. By utilizing critical data stored in the hardened memory, ZEDAC provides superior error detection and correction compared to standalone hardware (e.g., TMR) or software-assisted solutions (e.g., SECDED with Hamming codes)